![]()

![]()

![]()

Use LEFT and RIGHT arrow keys to navigate between flashcards;

Use UP and DOWN arrow keys to flip the card;

H to show hint;

A reads text to speech;

49 Cards in this Set

- Front

- Back

|

Analog and digital signals ? |

Analog : is a continuous wave form that change smoothly over time Digital : is discrete. It can have only a limited number of defined values. Often as 1 or 0 |

|

|

Maximum count formula ? |

2^n-1 |

|

|

vcc and ground #s |

14 = vcc 7 = ground |

|

|

Basic Boolean algebraic identities Additive A+0=? A+1= A+A= A+ A(not) = Multiplicative 0xA= 1xA= AA= AA(not)= |

Additive 0 1 A 1 Multiplicative 0 A A 0 |

|

Front (Term) |

Back (Definition) |

|

Front (Term) |

Back (Definition) |

|

Front (Term) |

None, anything over 9 is invalid |

|

|

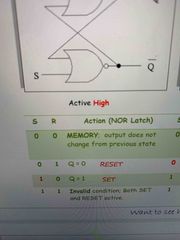

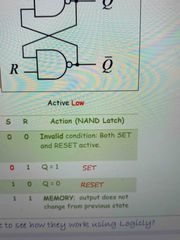

SR latch What gates does active low & active high have ? |

Active low=Nand gates Active high = Nor gates |

|

|

Active high Memory ? Reset? Set Invalid ? |

|

|

|

Active low Memory ? Reset? Set? Invalid |

Back (Definition) |

|

Front (Term) |

Back (Definition) |

|

|

D - flip flop What’s the most important thing to remember |

Q follows d - but only on the clock |

|

|

J K flip flop 1)J = 0 k=0 = ? 2) J=0 k=1 =? 3) J= 1 k= 0 = ? 4) J= 1 k= 1 =? |

1) memory 2) reset 3) set 4) toggle |

|

|

1) Asynchronous inputs are used for what? 2) The preset and clear input make Q change instantly cause why? |

1) used to override the clock / data inputs and force the outputs to a predefined state 2) they’re above the clock |

|

|

TTL ICS Power supply ? Logic Low ? Logic high? Undefined zone? And why? |

+5v 0-0.8v 2-5v 0.8-2v undefined - such voltages cause unpredictable results and problems for logic circuits |

|

|

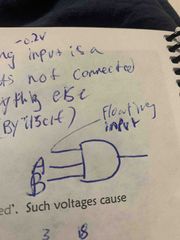

Floating inputs in TLL & CMOS In TTL ? In CMOS ? |

In TTL. IC behaves if it had a input of 1 on the floating input In CMOS, IC doesn’t clearly see the floating input as being either a 1 or 0. A floating input to a cmos logic gate may create excessive temperature rise and cause the gates destruction |

|

|

For AND & NAND floating input is connected to ? For OR or NOR the unused inputs are connected to? |

AND & NAND = Vcc OR & NOR = ground |

|

|

If the input clock frequency to the a ripple up- counter was 1,000,000hz. What’s the frequency output? |

D) 1000000/ 16 = 62.5khz |

|

|

How would you create a MOD -6 |

Back (Definition) |

|

Front (Term) |

Back (Definition) |

|

|

Parallel-in parallel out (PIPO) shift register Advantages? |

Fast! With the single clock pulse, all bits are transferred |

|

|

Four main types of flip flops ? |

SR Data JK Clocked SR |

|

|

What makes a flip flop synchronous ? |

Clock input |

|

|

Clocked j-k flip flop in normally used in the what mode when j-k being both high? |

Toggle mode |

|

|

In the set mode, the Q output of the flip flop is logic level? |

1 |

|

|

Inputs preset & clear are called what |

Asynchronous. They don’t require a clock to function. They overide the clock |

|

|

What’s the functions of preset & clear inputs ? |

Preset to make Q=1 Set to make the Q=0 |

|

|

Flip - flops are wired together to form what kind of device ? |

Counter & shift registers |

|

|

Name one application of the simple SR flip - Flop |

Switch de-bouncer |

|

|

In the toggle mode, how is the output frequency of the Q output related to the clock pulse frequency in the J-K flip flop? |

Frequency of Q= frequency of clock + 2 |

|

|

CMOS ? CMOS can operate a supply voltage between ? Logic low percentage ? Logic high percentage ? |

Supply voltage = 3-18 Low :30% High :70 % |

|

|

CMOS if you were supplying a voltage of 15v What would be the logic high and low for that supply. What’s it’s undefined region? |

Logic low = 0-4.5 v Logic high = 10.5-15v Undefined region = 4.5v-10.5v |

|

|

Floating input? |

It’s a input that’s not connected to anything else |

|

Front (Term) |

In Calculator 168 to binary = 10101000 Since it says 6 flip-flops, you keep six of the last binaries. = 101000 |

|

|

Shift register used ? |

Used for data storage or for the movement of data |

|

|

Synchronous counters have their clocks inputs connected in |

Parallel |

|

|

What’s the purpose behind adding gates to flip flops used in binary ripple counters ? |

Stopping a count…. Forcing it to recycle |

|

|

What’s the largest binary number a modulus -16 will count to |

1111 which is 15 |

|

|

Two disadvantages of serial in / serial out ? |

2) In order to transfer a nibble of data (4-bits) FOUR shift pulses are required ( slow) 2) After each shift pulse the data stored in the last register is lost as it’s shifted out |

|

|

Parallel in / parallel out register may be used to store ? |

Binary data |

|

|

PIPO 1) data is normally transferred within a computer in parallel to allow ? 2) data is stored in parallel format because this allows high-speed read operations to? |

1) allow high-speed data transfer 2) be performed by the computer |

|

|

True or false ? SI/SO registers destroy the data bits as they are shifted out of the register |

True |

|

|

1) Shift register is made up by primarily of ? 2) an 8-but shift register has a storage capacity of ? 3) for an 8-bit serial input register, the number of data bits that can be entered on each clock pulse is ? |

1) flip-flops 2) 1 byte 3) eight |

|

|

1) Shift register is made up by primarily of ? 2) an 8-but shift register has a storage capacity of ? 3) for an 8-bit serial input register, the number of data bits that can be entered on each clock pulse is ? |

1) flip-flops 2) 1 byte 3) eight |

|

|

1) For a parallel input shift register, the number of data bits that can be entered on each clock pulse? 2) to serially shift byte of data into a 8 bit shift register, there must be ? |

1) depends on the number of flip flops 2) eight clock pulses? |

|

|

1) A register is a group of latches or flip-flops used to transfer, store or shift data. True or false ? 2) what type of register would be used to take parallel data from within a digital system and convert it to a format for transmission over a single line ? |

1) true 2) parallel in / parallel out |

|

|

Data transformed out a parallel in / parallel out register are normally destroyed ? |

False |

|

|

Nanoseconds for TTL & CMOS |

TTL= 5-10 nanonseconds Cmos = 30-40 nanoseconds |

|

|

What type of flip flop do shift registers use |

D- type flip flops |